在电子设备向小型化、高集成度升级的当下,高密度、细间距电路板已成为行业主流。这类电路板凭借更高的元件封装密度、更窄的引脚间距,实现了设备性能的跨越式提升,但也给焊接环节带来了诸多“老大难”问题——虚焊、连锡、桥连频发,焊点可靠性不足,批量生产良率难以保障。其实,这些问题的根源多在于设计阶段的细节疏忽,通过针对性的设计优化,就能从源头攻克焊接难题,本文结合实战经验,拆解高密度、细间距电路板的焊接友好型设计方案。

高密度、细间距电路板的焊接痛点具有鲜明特殊性。一方面,引脚间距从传统的0.5mm缩减至0.3mm甚至0.2mm,焊盘与引脚的对位容错率极低,稍有设计偏差就会导致连锡;另一方面,元件密集导致散热速度快,焊接时热量难以集中,易出现假 焊、冷焊;同时,细小焊盘的焊膏量控制难度大,过多易溢胶搭桥,过少则无法形成可靠焊点。这些问题相互叠加,使得焊接良率成为制约产品量产的关键瓶颈,而设计阶段的优化正是解决这些问题的核心突破口。

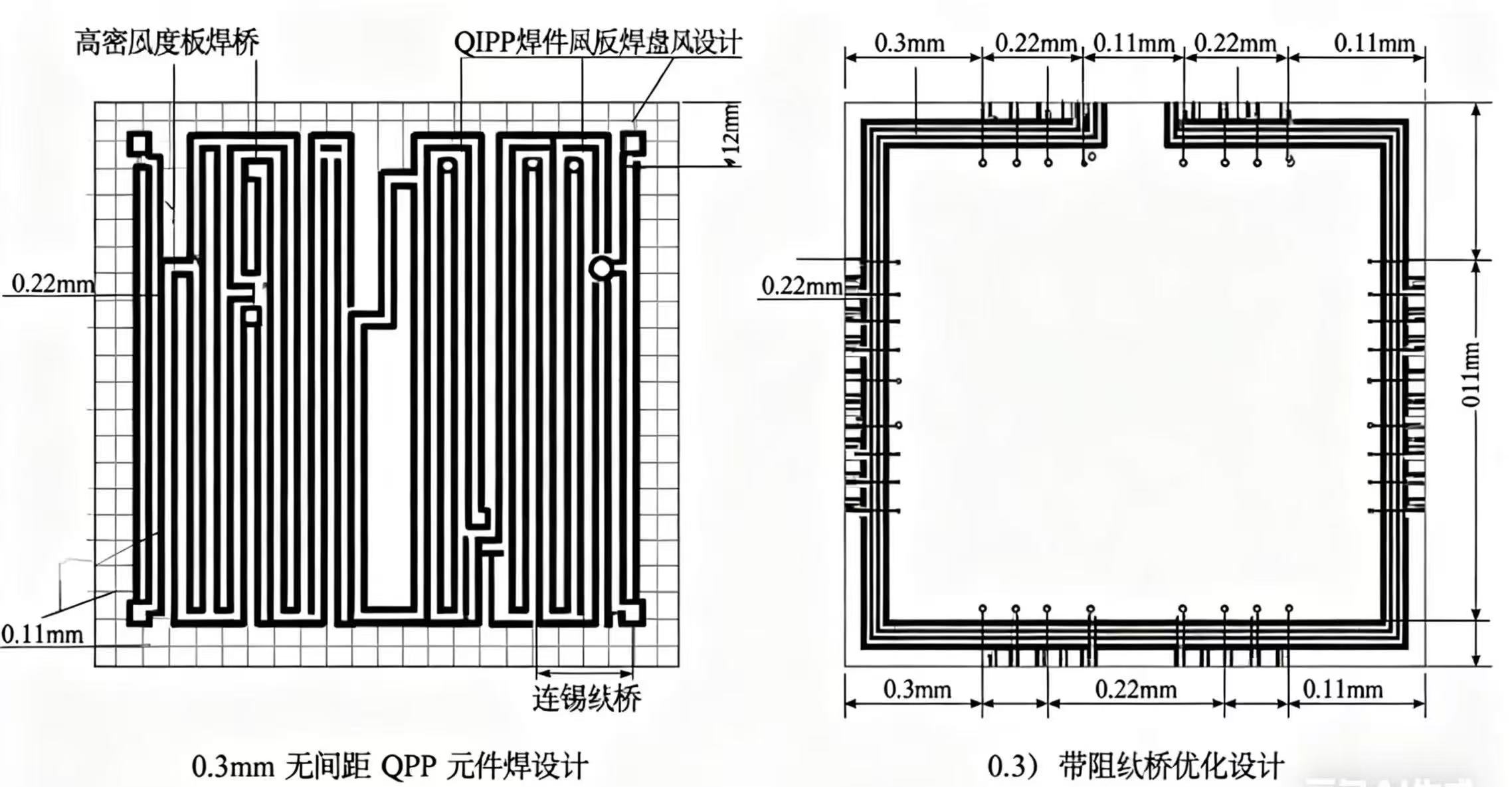

焊盘设计是决定焊接效果的基础环节,需精准匹配细间距元件特性。对于QFP、BGA等细间距封装,焊盘尺寸必须严格遵循“引脚宽度的70%-80%”原则,例如0.3mm引脚间距的元件,焊盘宽度应控制在0.21-0.24mm,既保证焊接时的润湿面积,又避免相邻焊盘间距过小导致连锡。焊盘形状设计同样关键,矩形焊盘更适合窄间距引脚,其长度方向与引脚延伸方向一致,可增加焊点附着力;对于拐角引脚,可采用圆角焊盘减少应力集中,降低后期脱焊风险。此外,焊盘间距需预留足够的“安全距离”,建议不小于0.1mm,若空间受限, 可通过优化阻焊开窗设计,利用阻焊剂隔离相邻焊盘,从物理层面避免连锡。

布局优化需兼顾焊接操作空间与散热均衡。高密度电路板布局时,应避免细间距元件与大体积发热元件直接相邻,两者间距至少预留3mm以上,防止焊接时热量被快速吸收,导致焊膏熔化不充分。同时,元件排列需为焊接工具预留操作空间,细间距元件周围不宜密集布置过高的连接器、电容等元件,建议预留至少2mm的“无遮挡区域”,方便烙铁头或回流焊热风精准作用于焊点。对于双面布局的电路板,应避免细间距元件上下层正对布置,减少焊接时的热干扰,降低底层焊点被二次熔化导致的脱焊风险。

热设计与焊膏兼容性优化是提升焊接可靠性的关键。高密度电路板的散热路径设计需科学合理,可通过增加散热铜皮、设置导热过孔等方式,使焊接热量均匀分布,避免局部温度过高导致元件损坏,或局部温度过低引发虚焊。在焊膏选择上,细间距焊接应优先选用颗粒度更细的焊膏(如Type4或Type5型),其流动性更好,能更均匀地覆盖细小焊盘;同时,焊膏的合金成分需与元件引脚、焊盘镀层匹配,例如对于镀锡引脚,可选用Sn63/Pb37合金焊膏,其熔点较低、润湿性能优异,能有效降低焊接难度。

DFM(面向制造的设计)规则落地是确保设计可制造性的核心。设计阶段需提前与生产部门沟通,明确焊接工艺参数,例如回流焊的温度曲线、波峰焊的传输速度等,使设计方案与生产工艺无缝衔接。对于细间距BGA元件,需在焊盘区域设计足够的测试点,方便焊接后的电气性能检测,避免因焊点隐藏导致的故障排查困难。此外,应避免在细间距元件焊盘附近设计过孔,若必须设置,需采用阻焊剂覆盖过孔,防止焊膏流入过孔造成焊量不足,影响焊点可靠性。

实战案例显示,某高密度控制板通过上述设计优化,焊接良率从65%提升至98%。该电路板原存在0.3mm间距QFP元件连锡、BGA元件虚焊等问题,优化后将QFP焊盘宽度调整为0.22mm,间距扩大至0.11mm,同时在元件周围预留2.5mm操作空间,选用Type5型细颗粒焊膏,并优化回流焊温度曲线,最终彻底解决了焊接难题。这一案例充分说明,高密度、细间距电路板的焊接问题并非不可攻克,关键在于将焊接需求贯穿设计全流程,通过精准的焊盘设计、合理的布局规划、科学的热设计与工艺匹配,从源头规避焊接风险。

总之,搞定高密度、细间距电路板的焊接“老大难”,核心在于“设计先行”。通过优化焊盘尺寸与间距、合理规划元件布局、匹配焊膏与工艺参数、落地DFM设计规则,就能有效降低连锡、虚焊、脱焊等风险,提升焊接良率与焊点可靠性。在电子设备集成度持续提升的趋势下,掌握这些设计优化技巧,将为产品量产与性能保障提供关键支撑。

凯胜电子为您提供从PCB线路板设计,PCB设计,PCB制作打样、PCBA加工、SMT贴片加工、电路板焊接、PCBA代工代料等一站式PCBA服务,为客户提供一条龙服务,让客户省心放心,同时也大大节约了客户的开发成本